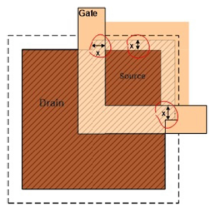

L Style n-MOSFET Layout for Mitigating TID Effects

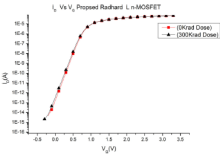

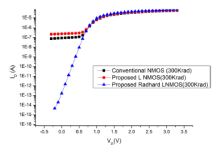

| Abstract | This paper proposes a new rad hard layout L style of nmos metal oxide semiconductor field effect transistor (n-MOSFET), which is evaluated to show that its efficacy at reducing radiation-induced leakage currents, thus improving the total ionization dose(TID) tolerance with very less area and parasitic capacitance as compared to enclosed layout transistor(ELT). This proposed layout structure is fully compatible to present commercial fabrication technology without any additional mask requirement as compared to conventional n MOSFET fabrication and can be used as radiation tolerant by design technique. The simulated ID - VG characteristics of the rad hard L n-MOSFET layout demonstrated the effectiveness of eliminating radiation-induced leakage current paths. The leakage current in proposed rad hard L n-MOSFET has been reduced by factor of 108 at 300Krad dose as compared to conventional layout n-MOSFET. |

| Faculty |

Prof. Neelam Rup Prakash

|

|

neelamrprakash@pec.edu.in

|

|

| More Information | https://link.springer.com/article/10.1007/s12633-021-01150-z |