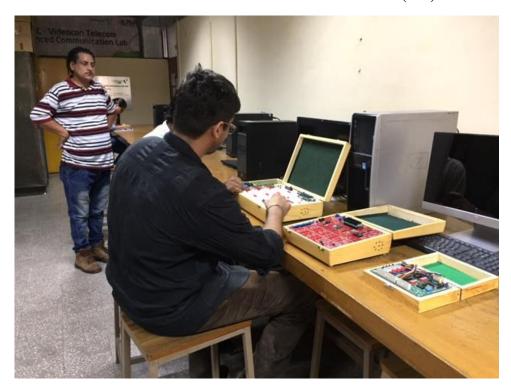

## ECE LAB- VIII: UG VLSI LAB / PROJECT LAB (UG)

## **Objective of the Laboratory:**

- Provide an overview of the fundamental principles of VLSI, ASIC / FPGA design.

- Give the understanding of the characteristics of CMOS circuit construction.

- Analyse the basic building blocks of large-scale digital integrated circuits.

- Help design functional units such as adders, multipliers, ROMs, and SRAMs.

## **Major Equipment:**

| Sr.<br>No. | Equipment Name      | <b>Equipment Description</b>                                                                                                                                                                                                                                                          |

|------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.         | Microwind 3.8       | Allows the student to design and simulate an integrated circuit at physical description level. It includes all the commands for a mask editor as well as original tools never gathered before in a single module (2D and 3D process view, Verilog compiler, tutorial on MOS devices). |

| 2.         | Quartus II          | This software enables creation and delivery of FPGA, CPLD and structures ASIC designs. The software support VHDL and Verilog HDL, design entry, graphical based design entry methods and integrated system level design tools.                                                        |

| 3.         | VLSI Trainer System | Universal Platforms for XILINX FPGA/CPLD devices.                                                                                                                                                                                                                                     |

| 4.  | VLSI Interface Board          | Provides a comprehensive, best-in-class design      |

|-----|-------------------------------|-----------------------------------------------------|

|     |                               | environment to develop a low-cost and low-          |

|     |                               | power system-level designs.                         |

| 5.  | Daughter board for FPGA       | SATA/SAS Daughter Card is designed to               |

|     | (ACEX) 1k50                   | provide SATA interface conversion for FPGA          |

|     |                               | platforms                                           |

| 6.  | Daughter board for FPGA       | Development and Education board is designed in      |

|     | (ACEX) ep20k                  | a compact size with all the essential tools for     |

|     |                               | novice users to gain knowledge in areas of digital  |

|     |                               | logic, computer organization and FPGAs              |

| 7.  | Daughter board for CPLD       | Development Board is designed to prototype          |

|     | (9EPM) 3128                   | most common FPGA applications (CPLDs).              |

| 8.  | Daughter board for CPLD       | Development Board is designed to prototype          |

|     | (EPM) 7128                    | most common FPGA applications (CPLDs).              |

| 9.  | Universal Communication       | Digital data in system can be encoded in several    |

|     | Development Kit               | formats                                             |

| 10. | GSM/GPRS Development          | Is complete tri-band GSM/GPRS solution in           |

|     | Board                         | compact plug-in module                              |

| 11. | Bluetooth Development         | Serial port Bluetooth module, can directly stack    |

|     | Board                         | on Arduino and use the UART port for Bluetooth      |

|     |                               | communication.                                      |

| 12. | GSM Development board         | Adding a remote monitoring and control to           |

|     |                               | remote places by a GSM cellular network.            |

| 13. | QAM                           | Initiates the user to various data conditioning and |

|     | Modulation/Demodulation       | carrier modulation techniques                       |

|     | Kit                           |                                                     |

| 14. | 2 Workstations & 8 Computer S | Systems                                             |

## Name of Officials handling Lab:

- 1. Dr. Jyoti Kedia (O/I)

- 2. Dr. Divya Dhawan (Joint O/I)

- 3. Mrs. Amita Chawla (Lab Foreman)

- 4. Mr. Rajesh Kumar (Lan Attendant)